3月初的时候,英特尔、AMD、Arm、高通、台积电、三星、日月光、谷歌云、Meta、微软等行业巨头组建了一个Chiplet标准联盟,并制定了一套通用的Chiplet高速互联标准“Universal Chiplet Interconnect Express”(简称:UCIe)。

Chiplet标准联盟的成立是一件意料之中的事情,而这个联盟的初始创建没有大陆芯片公司同样不会让人感到意外。虽然已经有芯原股份宣布加入了这个联盟,但该联盟由谁主导也是显而易见的。在当前的国际竞争格局下,大陆芯片产业是一个特殊的存在,被美欧日韩等半导体巨头处处提防。

那么,大陆是否有必要去构建一套自己的Chiplet标准呢?让我们通过常用的SWOT分析法,来具体看一下这种做法的可行性和利弊。

Chiplet需要标准

Chiplet的中文名是芯粒或者小芯片。通过下图能够看到,Chiplet这项技术有四个核心的构成部分,分别是基础功能芯片、具备特定功能的裸片(die)、die-to-die内部互联技术以及特定的封装技术。

图源:ODSA工作组

Chiplet的好处是显而易见的。首先,die的复用能够降低系统复杂度,降低研发成本;其次,芯片性能的提升不再是只能依靠摩尔定律;第三,功能单元模块化提高了芯片的制造良率,进而降低制造成本;第四,Chiplet给了封装产业一个明确的创新方向。英特尔首席架构师沙尔玛在UCIe联盟官网发布的白皮书中这样总结Chiplet的商业价值,“从设计角度看,能够有效降低投资,节省不必要的跨工艺节点IP移植成本,缩短产品上市周期;从制造角度看,有利于制造环节良率控制、产能爬坡;从产品角度看,不同计算、存储、I/O芯片(die)的灵活组合,使敏捷芯片定制成为可能。”

那么很显然,Chiplet是需要一套通用标准的,关于die的尺寸,关于die-to-die如何互联,关于封装后的接口IP如何布局,关于如何部署测试机台等等。如果没有标准,Chiplet便会成为一次又一次的ASIC设计,省不下多少功夫,更形不成规模产业,也就不是一门好生意。

比如,现阶段AMD和苹果会采用Chiplet的方式去构建芯片,虽然明面上看着成本会有所下降,因为很多功能单元是此前就设计好的,但背后的IC设计、封装和测试成本都非常高。并且,在没有标准的情况下,选定了哪一家的die就真的是选定了,后面看到了更好的也换不起,因为一个功能单元的替换,可能就意味着整颗芯片的重新设计。

在摩尔定律明显放缓的当下,Chiplet一定是产业的发展趋势,但是要让Chiplet成为一个规模产业,标准是必不可少的。

但是,以美国为首的国际半导体厂商当然不想有大陆芯片公司在所谓的“开放”的UCIe标准中起到主导作用,那么大陆是否要自己搞一套呢?接下来进入SWOT分析环节。

大陆建Chiplet标准的优势(S)

美国有苹果、英特尔和AMD等公司搞Chiplet,大陆也并非只能在边上看着不做事,实际上华为此前就公布过“芯片堆叠技术”相关的专利,其实就是Chiplet类似的技术,清华大学微电子所所长、中国半导体行业协会副理事长魏少军教授也曾多次在公开演讲中提到过芯片封装从2.5D向3D的演进,芯原股份创始人、董事长兼总裁戴伟民博士更是力推Chiplet,大陆其实更早之前就成立过Chiplet联盟,说明大陆的科技公司以及从业者是重视Chiplet的。

如果大陆自己建一套Chiplet标准,是否有自己的优势所在?

我想大陆的优势主要会有两点,其一是大陆现阶段已经拥有从IC设计到封装测试这样完备的产业链基础,且大陆在封装环节的实力处于全球领先水平。当前,大陆在封装环节拥有长电科技、通富微电、华天科技三大龙头企业,根据2021年Q1的公开营收数据,三家厂商均是全球前十的水平,其中长电科技排名第三位。

其二是大陆拥有更好的应用市场,通过上方ODSA工作组分享的Chiplet概念图可以看到,Chiplet是在芯片设计制造环节提出了一个可行路线,而其还需要软件、设计工具等的配合,最后应用到终端市场。那么,终端市场具有一定规模且明确的需求便能够促进Chiplet的发展,对基于此打造出来的系统级芯片有带动作用。

大陆建Chiplet标准的劣势(W)

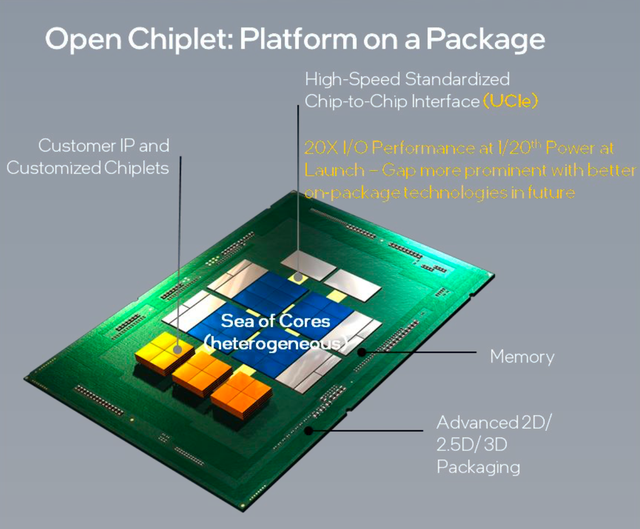

在探讨大陆自己建Chiplet标准的劣势之前,我们看一下另一张图片。下图来自UCIe联盟的示意图,就像我们上面提到的,这里面会有基础的核心芯片,也会有一些特定功能的die,以及各种连接协议,包括芯片内部的和外部的。

图源:UCIe联盟

那么大陆芯片产业的劣势就显露出来了。由于大陆现阶段芯片制造工艺和核心芯片的性能都不强,因此可以说基础不牢靠,Chiplet主要面向高性能的系统级芯片,那么在高性能这一点上大陆芯片产业现状还不达标。其实大陆现在能够达到国际领先水平的芯片并不多,大部分芯片还混迹在中低端,那么die的性能也会拖后腿。

另外还有我们常常提到的IP和EDA环节,下图是AMD在介绍Chiplet技术时用到的示意图,很显然Chiplet这种组装的方式在单个功能块上的制造难度会显著降低,但在系统层面还是需要将这些功能块组合起来,并且可能出现3D堆叠的效果,这需要更加智能化的EDA工具和IP支持,但这一块长期以来都是国内的薄弱环节。

图源:AMD

因此,国际EDA工具提供商是否配合大陆的Chiplet标准也是一个问题。

大陆建Chiplet标准的机会(O)

SWOT中的“O”代表机会,通常是分析外部环境,在此我们可以提一下目前的大环境。

Chiplet的好处显而易见,一定是一个产业趋势,且必将在芯片产业发挥重要的作用,这是毋庸置疑的,因此拥抱Chiplet也就成为一个必然的结果。而目前的国际形势也表明,传统的国际半导体巨头并不想带着我们一起玩,这些积极的和消极的因素都提供了大陆自己搞Chiplet标准的契机。

在机会这里我们必须还要重提摩尔定律失速,这也是国际半导体巨头抱团搞Chiplet标准的重要原因,在大陆芯片制造被高端光刻机“扼住咽喉”的时候,规模量产10nm以下工艺的芯片看似遥遥无期,那么Chiplet这种能够放大工艺效益的技术就应该去搞。

另外,在大的产业环境里,除了讲Chiplet,先进封装本身就是一个大方向,而Chiplet会起到积极的促进作用,从这个层面看,大陆想稳固芯片封装方面的优势,也得参与到Chiplet中来。

大陆建Chiplet标准的威胁(T)

在SWOT分析方法中, “T”代表威胁。那么,这个“威胁”实际上就是如果我们搞了自己的Chiplet标准,会面临哪些外部的冲击。笔者认为,威胁可以归结为可能存在的制裁,包括可能存在美政府要求使用美国技术的公司不为大陆Chiplet标准联盟成员提供产品和技术支持,以及对联盟成员的其他制裁措施。

Chiplet是一个产业链协作的创新技术,而在这个链路上,大陆芯片产业处处存在后发的弱势,每一项都可能带来巨大的威胁。

关于Chiplet的争论

实际上,国内早就有Chiplet联盟,由芯动科技和清华大学人工智能交叉研究院发起,目标正是推动Chiplet技术的国产化进程。据悉,目前国内已经制定了自己的chiplet标准草案,名为《小芯片接口总线技术要求》,由中科院计算所、工信部电子四院和国内多个芯片厂商合作展开标准制定工作,是一个较为纯粹的die-to-die连接协议,即将完成后续意见征询、技术验证和发布的工作。

我们从知情人士的透露获知,国内的标准出发点是自主原生,那么必然和UCIe标准存在差异化,算是迈开了第一步。但与此同时,质疑声也不小,Chiplet技术的出发点是为了让高性能运算芯片的成本降低,要是生硬地被走成国产芯片的自主化道路,是否丢掉了这项技术最大的价值,是否有些本末倒置?

古人云:乱世用重典,沉疴下猛药。但古人还说过,竭泽而渔。底层基础决定上层建筑,拉着国内目前领先厂商搞一个自己的Chiplet标准,投入产出比想来不会高,且尤为重要的EDA工具由谁来配合也是一个问题。我觉得现阶段国内当然要研究Chiplet技术,成立联盟和协会都没有问题,但并不急着搞一套自己的标准去做对抗,这样做多少有点闭门造车的意思。